# Pulse Control LSI PCL6046 User's Manual

# INDEX

| 1. Introduction                                     | 1  |

|-----------------------------------------------------|----|

| 1.1 How to use this manual                          | 1  |

| 1.1.1 Symbol description                            |    |

| 1.1.2 Terminology                                   |    |

| 1.1.3 Notation<br>1.2 Handling the product          |    |

|                                                     |    |

| 1.2.1 Storing                                       |    |

| 1.2.2 Unpacking<br>1.2.3 Safety                     |    |

| 1.3 Product Warranty                                |    |

| 1.3.1 Warranty period                               |    |

| 1.3.2 Warranty scope                                |    |

| 1.4 Notice                                          |    |

| 1.5 Confirmation                                    | 9  |

| 2. Outline                                          |    |

| 2.1 Features                                        |    |

|                                                     |    |

| 2.2 Configuration                                   |    |

| 3. Specifications                                   |    |

| 4. Hardware description                             | 17 |

| 4.1 External dimensions                             | 17 |

| 4.2 Pin assignment diagram                          | 18 |

| 4.3 Functions of pins                               | 19 |

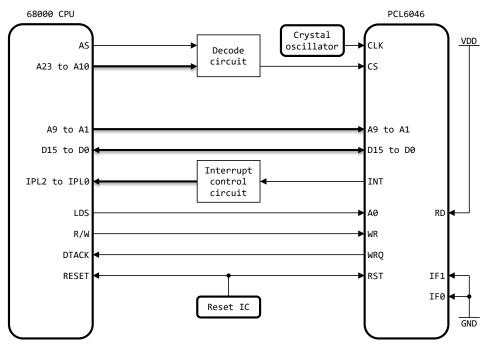

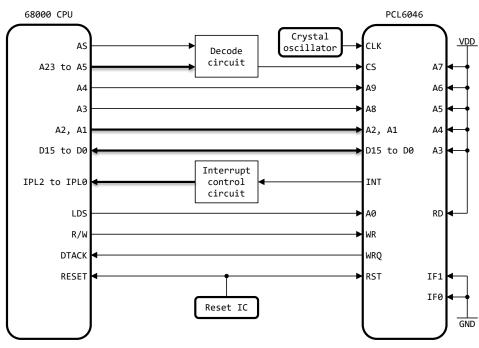

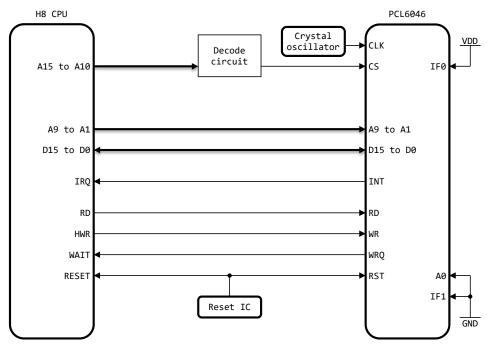

| 4.4 CPU interface                                   | 24 |

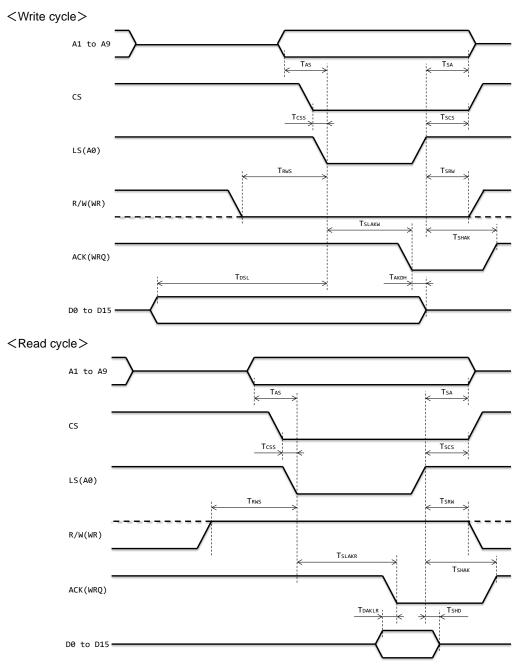

| 4.4.1 68000 interface                               | 25 |

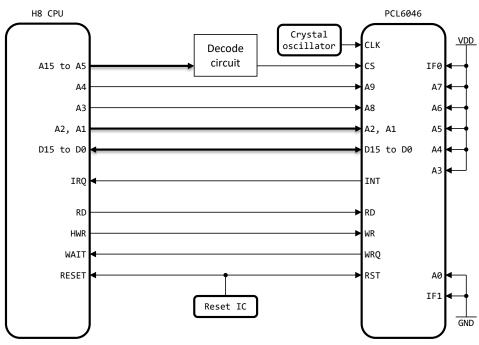

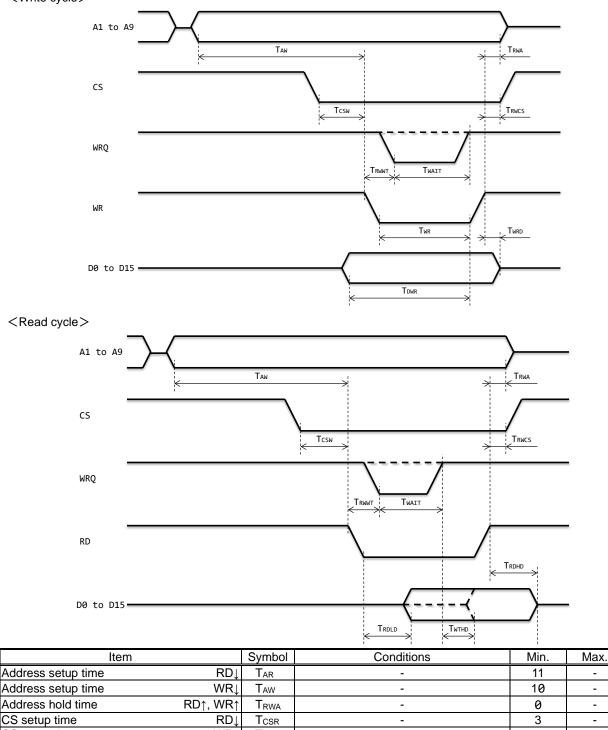

| 4.4.2 H8 interface                                  |    |

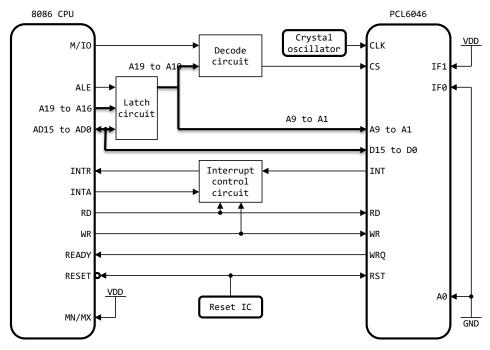

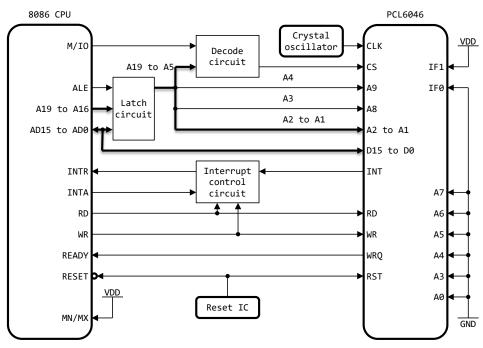

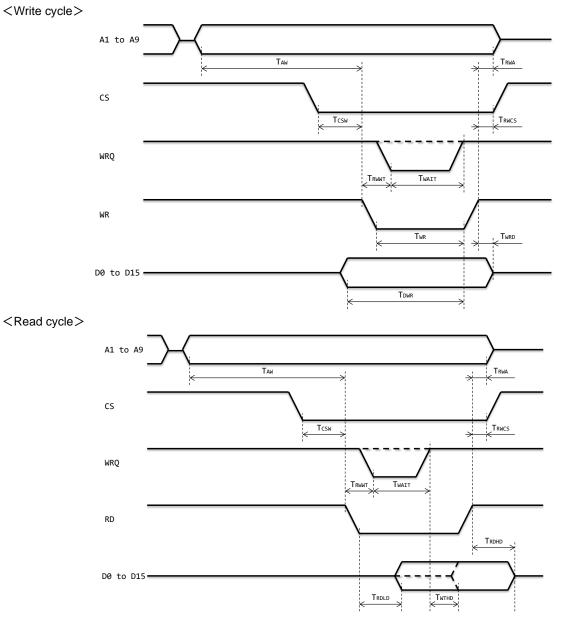

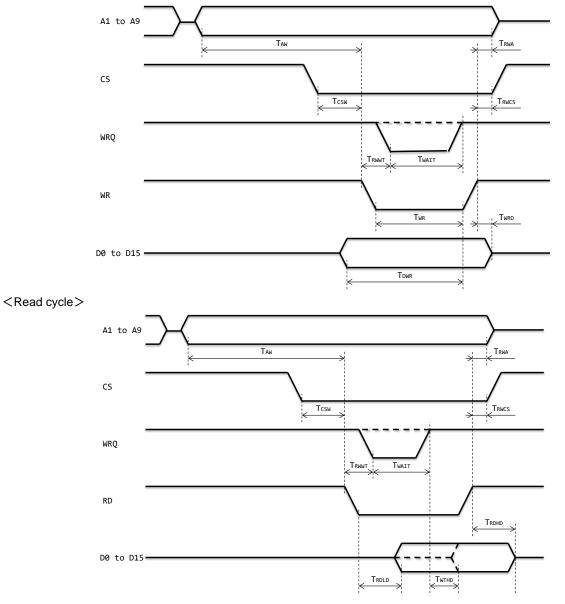

| 4.4.3 8086 interface                                |    |

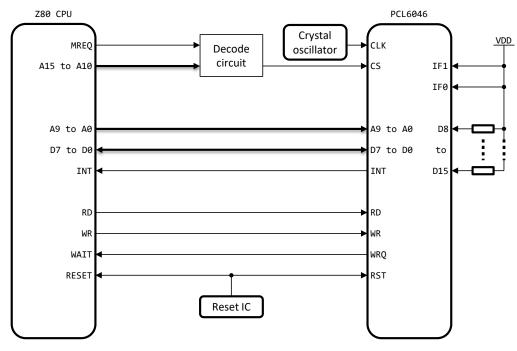

| 4.4.4 Z80 interface                                 |    |

| 5. Software description                             | 29 |

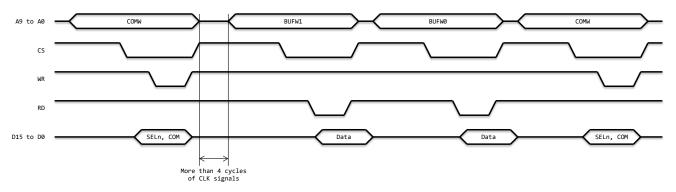

| 5.1 CPU communication                               |    |

| 5.1.1 Access method                                 |    |

| 5.1.2 Address map                                   |    |

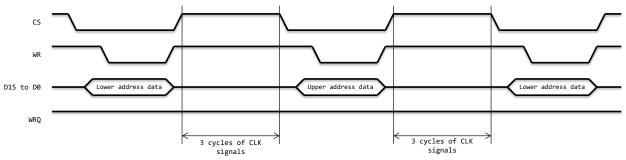

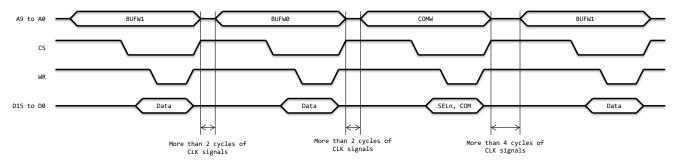

| 5.1.3 Command writing                               |    |

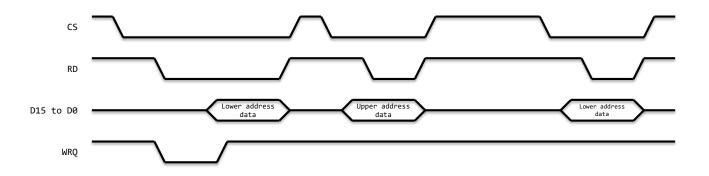

| 5.1.4 Register writing<br>5.1.5 Register reading    |    |

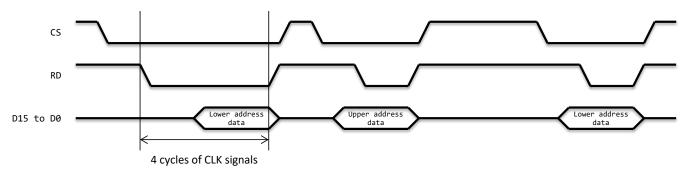

| 5.1.6 Main status reading                           |    |

| 5.1.7 General-purpose output port writing           |    |

| 5.1.8 Sub-status & general purpose I/O port reading |    |

| 5.2 Status & General-purpose I/O Port                               | 49  |

|---------------------------------------------------------------------|-----|

| 5.2.1 Main status (MSTS)                                            |     |

| 5.2.2 Sub status (SSTS) and general-purpose input/output port (IOP) |     |

| 5.2.3 Extension status (RSTS)                                       |     |

| 5.2.4 Interpolation status (RIPS)                                   | 53  |

| 5.3 Commands                                                        | 54  |

| 5.3.1 Operation commands                                            | 54  |

| 5.3.2 Control commands                                              |     |

|                                                                     |     |

| 5.4 Registers                                                       |     |

| 5.4.1 Speed control registers                                       |     |

| 5.4.2 Position control register                                     |     |

| 5.4.3 Environment setting register                                  |     |

| 5.4.4 Counter register                                              |     |

| 5.4.5 Comparator register                                           |     |

| 5.4.6 Counter latch register                                        |     |

| 5.4.7 Interrupt control register                                    |     |

| 5.4.8 Status display register                                       | 104 |

| 5.5 Operation mode                                                  | 108 |

| 5.5.1 Command control                                               |     |

| 5.5.2 Positioning control                                           |     |

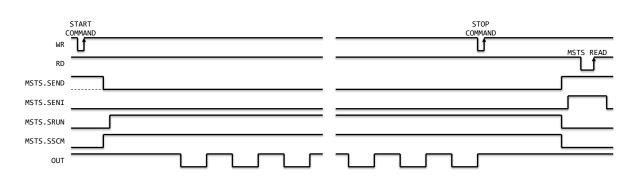

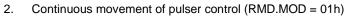

| 5.5.3 Pulser control                                                |     |

| 5.5.4 Switch control                                                |     |

| 5.5.5 Origin return control                                         |     |

| 5.5.6 Sensor control                                                | 141 |

| 5.5.7 Linear interpolation 1 control                                | 144 |

| 5.5.8 Linear interpolation 2 control                                | 146 |

| 5.5.9 Circular interpolation control                                |     |

| 5.5.10 U-axis synchronous control                                   |     |

| 6. Function description                                             |     |

| 6.1 Reset                                                           |     |

|                                                                     |     |

| 6.1.1 Hardware reset                                                |     |

| 6.1.2 Software reset                                                | 154 |

| 6.2 Pre-register                                                    | 155 |

| 6.2.1 Continuous operation                                          | 155 |

| 6.2.2 Continuous comparison                                         | 157 |

| 6.3 Speed control                                                   |     |

| 6.3.1 Speed patterns                                                | 150 |

|                                                                     |     |

| 6.3.2 Speed setting example                                         |     |

| 6.3.3 Manual correction calculation of FH speed                     |     |

| 6.3.4 Target speed override                                         |     |

| 6.3.5 Number of circular interpolation steps                        |     |

| 6.3.6 Constant synthesized speed control                            |     |

| 6.4 Position control                                                |     |

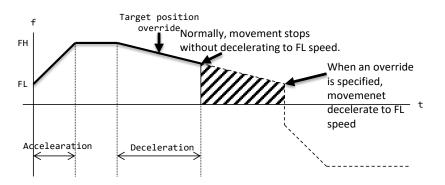

| 6.4.1 Target position override 1 (RMV)                              | 169 |

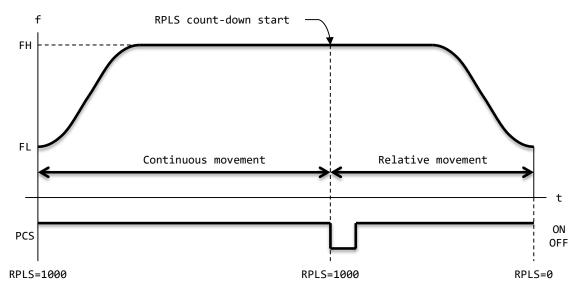

| 6.4.2 Target position override 2 (PCS)<br>6.4.3 End point draw operation                                                                                                                                                               |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

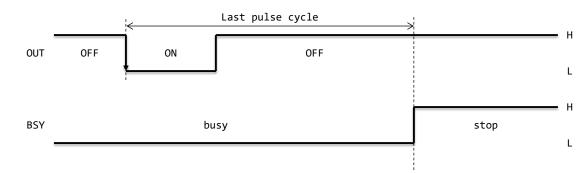

| 6.5 Output pulse control                                                                                                                                                                                                               | 174 |

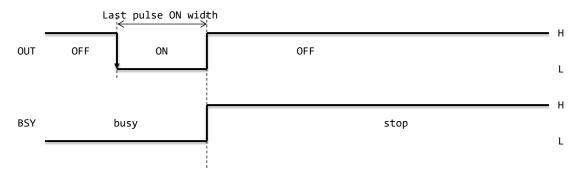

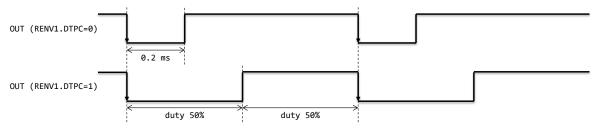

| <ul><li>6.5.1 Output pulse mode</li><li>6.5.2 Operation complete timing</li><li>6.5.3 Output pulse width control</li></ul>                                                                                                             | 175 |

| 6.6 Idling control                                                                                                                                                                                                                     | 177 |

| 6.7 Mechanical external input control                                                                                                                                                                                                  |     |

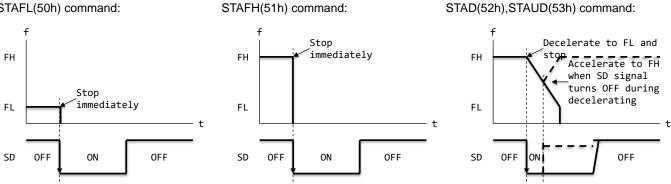

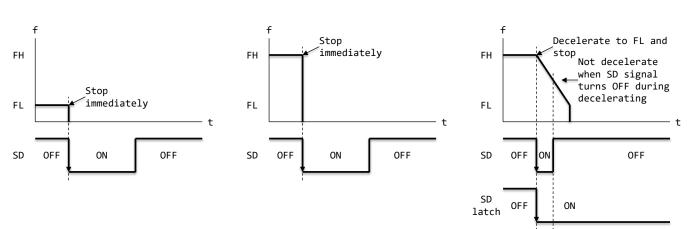

| 6.7.1 End limit (+EL, −EL)<br>6.7.2 Slow-down (+SD, −SD)<br>6.7.3 Origin (ORG), Encoder Z phase (EZ)                                                                                                                                   |     |

| 6.8 Servo motor interface                                                                                                                                                                                                              |     |

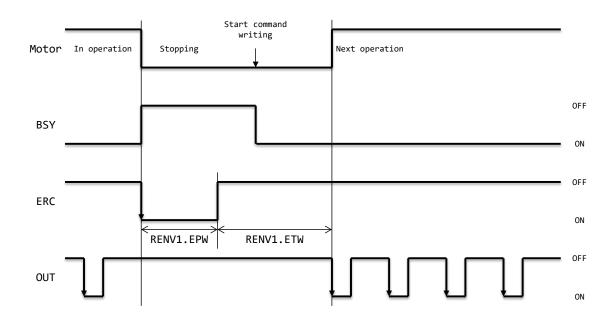

| <ul><li>6.8.1 Positioning complete (INP)</li><li>6.8.2 Deviation counter clear (ERC)</li><li>6.8.3 Alarm (ALM)</li></ul>                                                                                                               |     |

| 6.9 External start / Simultaneous start                                                                                                                                                                                                |     |

| <ul><li>6.9.1 Simultaneous start (CSTA)</li><li>6.9.2 Own axis start (STA)</li><li>6.9.3 Axis selection start (SELn)</li></ul>                                                                                                         |     |

| 6.10 External stop / Simultaneous stop                                                                                                                                                                                                 |     |

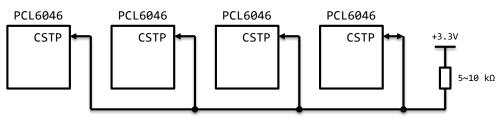

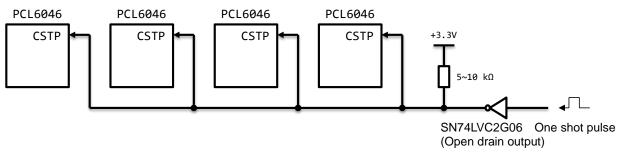

| 6.10.1 Simultaneous stop (CSTP)<br>6.10.2 Axis selection stop (SELn)                                                                                                                                                                   |     |

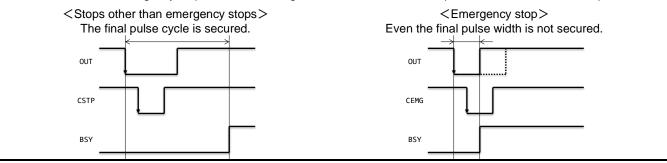

| 6.11 Emergency stop                                                                                                                                                                                                                    | 195 |

| 6.12 Counter                                                                                                                                                                                                                           |     |

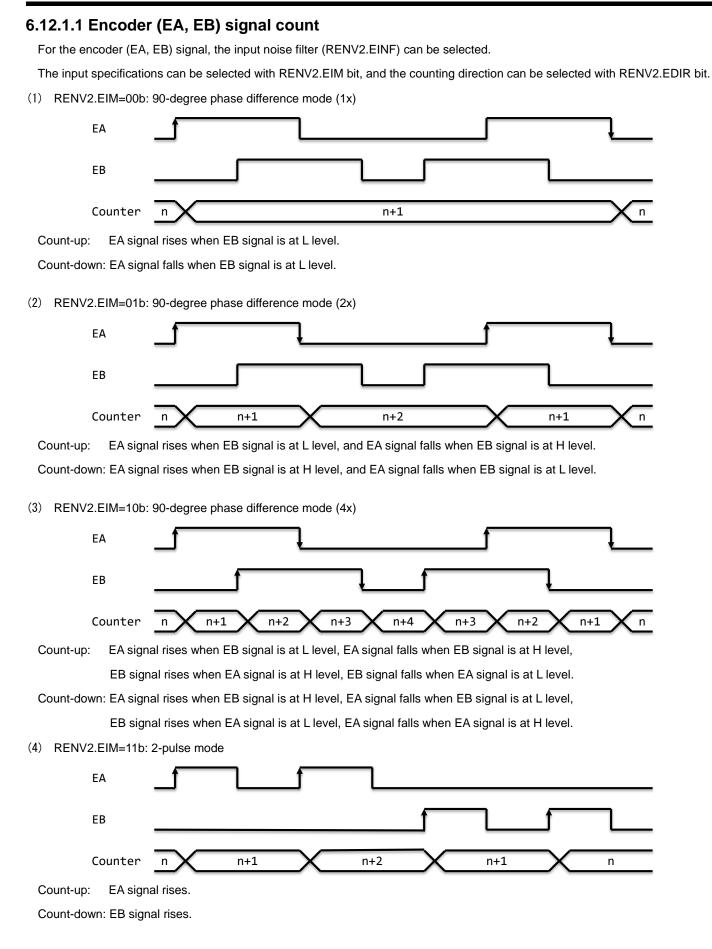

| <ul> <li>6.12.1 Counter type and input specifications</li> <li>6.12.2 Counter clear</li> <li>6.12.3 Counter latch</li> <li>6.12.4 Counter count stop and input stop</li> </ul>                                                         |     |

| 6.13 Comparator                                                                                                                                                                                                                        |     |

| <ul> <li>6.13.1 Comparator types and functions</li> <li>6.13.2 Software limit</li> <li>6.13.3 Out-of-step detection of stepping motor</li> <li>6.13.4 Index output</li> <li>6.13.5 Ring count</li> <li>6.13.6 Bulk override</li> </ul> |     |

| 6.14 Backlash correction                                                                                                                                                                                                               |     |

| 6.15 Slip correction                                                                                                                                                                                                                   | 230 |

| 6.16 Vibration suppression                                                                                                                                                                                                             | 231 |

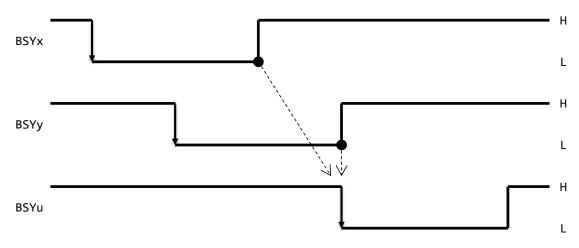

| 6.17 Synchronous start                                                                                                                                                                                                                 | 232 |

| 6.17.1 Start by stopping the specified axis<br>6.17.2 Start with internal sync signal                                                                                                                                                  |     |

|                                                                                                                                                                                                                                        |     |

| 244 |

|-----|

|     |

| 245 |

| 246 |

| 247 |

| 248 |

| 249 |

| 249 |

| 249 |

| 250 |

| 250 |

|     |

| 251 |

| 252 |

| 253 |

| 254 |

| 255 |

|     |

| 256 |

| 256 |

| 257 |

| 257 |

| 257 |

|     |

# 1. Introduction

Thank you for choosing our pulse control LSI, the "PCL6046."

This manual describes the specifications, functions, connections, and usages of PCL6046.

Be sure to read this manual thoroughly and keep it handy in order to use the product appropriately.

# 1.1 How to use this manual

- 1. Reproduction of this manual in whole or in part without permission is prohibited by the Copyright Act.

- 2. The contents of this manual are subject to change without the prior notice along with the improvement of performance and quality.

- 3. Although this manual is produced with the utmost care, please contact our sales representative if there are any questions, errors or omissions.

# 1.1.1 Symbol description

### 1.1.1.1 Physical damage level

In this manual, the physical damage level is defined as follows.

Serious injury

Those that might cause aftereffects such as loss of sight, wound, burn, electric shock, fracture, poisoning, or those requiring hospitalization or long-term outpatient treatment.

Minor injury

Those not requiring hospitalization or long-term outpatient treatment. (Other than "serious injury" above)

#### 1.1.1.2 Hazardous level

The product is designed with the top priority for the safety of operators. However, due to the nature of the product, there are risks that cannot be eliminated. In this manual, the seriousness and level of these risks are divided into three categories:

"Danger," "Warning," and "Caution." Be sure to read and understand the symbols descriptions thoroughly before operating or performing maintenance work on the product.

"Danger", "Warning", and "Caution" are indicated in the order of severity of hazard: (danger > warning > caution), and the meanings are described underneath.

### 🥼 Danger

"Danger" indicates that it might cause an imminent risk that could result in the death or serious injury of the operator during operations of this product.

Warning

"Warning" indicates that it may result in the death or serious injury of the operator during operations of this product.

Δ

### 🛕 Caution

"Caution" indicates that it may result in minor injury of the operator during operations of this product.

| Caution                                                                                                                                                                                         |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| "Caution" without warning symbol indicates that the operator is not likely to be injured, but it can cause damage result in a malfunction to this product, your equipment, or your instruments. | e or |

In addition to the hazardous level classifications described above, the following notations are also used.

#### I m p o r t a n c e

"Importance" indicates the information and contents that must be known particularly in operations and maintenance works of this product.

| Rema | r | k | S |

|------|---|---|---|

|------|---|---|---|

"Remarks" initiates the useful information or contents for operations and maintenance works of this product.

#### 1.1.1.3 Warning symbol

In this manual, the following symbols are added along with the notations "Danger," "Warning," "Caution," and "Importance" to indicate the warning contents in an easy-to-understand manner.

This symbol indicates that a high voltage may be applied.

Failure to confirm safety or mishandling of this product might cause a risk

of electric shock, burn, or death.

This symbol indicates that some parts have a high surface temperature, and the mishandling can cause a risk of burns.

This symbol indicates that mishandling may cause a fire.

This symbol indicates "prohibited" actions that must not be performed in

the operation and the maintenance work of this product.

This symbol indicates "mandatory" actions that must be performed in the operation and the maintenance work of this product.

### 1.1.2 Terminology

Terminology used in this manual is described below.

Refer to our web pages for terms that are not described in this section.

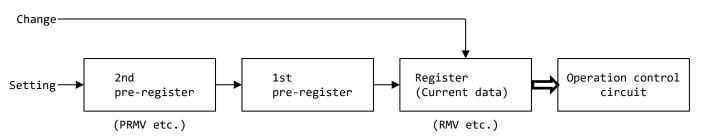

#### • 1st pre-register (= Pre-register)

Pre-register is a register to set the continuous operation data during operation. It exists for every function such as for positioning control, speed control, and the like. When the operation mode is completed, each pre-register value will be copied to the current register at the same time so as to start the next operation mode.

#### • 2nd pre-register

This register is provided in the previous stage of 1st pre-register, which is a register for setting continuous operation data. Usually, if the 2nd pre-register is available, you write to the current register or 1st pre-register via the 2nd pre-register.

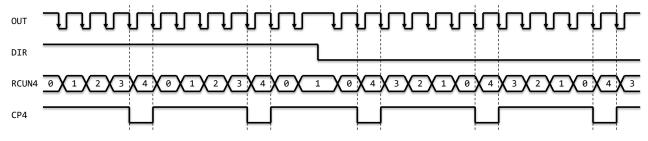

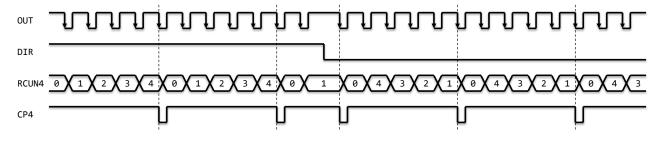

• Common-pulse mode (OUT, DIR)

One of the output forms of pulse signals for driving a motor. Output pulse signals (OUT) and direction signals (DIR) are output.

• 2-pulse mode (PLS, MNS)

One of the output forms of pulse signals for driving a motor. Plus direction pulse signals (PLS) and Minus direction pulse signals (MNS) are output.

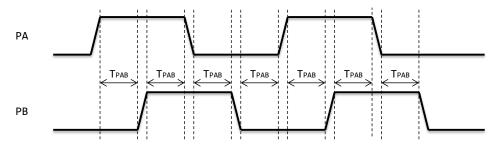

• 90-degree phase difference mode (PHA and PHB)

One of the output forms of pulse signals for driving a motor.

A-phase pulse signals (PHA) and B-phase pulse signals (PHB) with 90-degree phase differences are output.

The signal frequency will be 1/4 of the operating speed of the motor.

Therefore, an inexpensive interface circuit can be used.

• CW

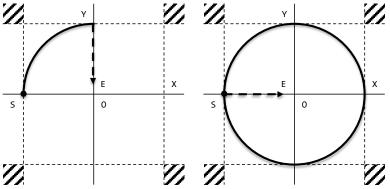

Clockwise.

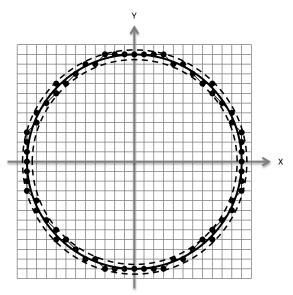

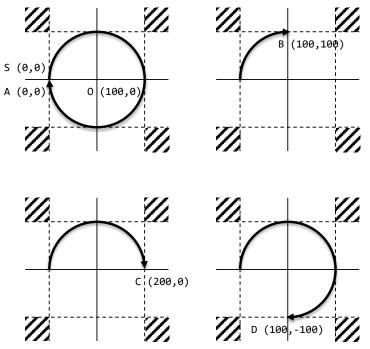

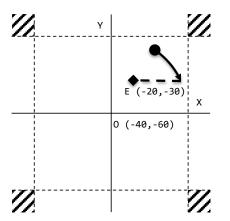

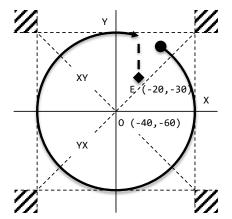

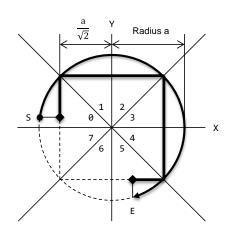

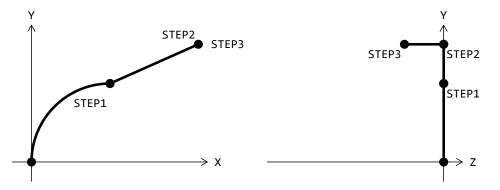

In CW circular interpolation, X-axis operates in the plus direction and Y-axis operates in the minus direction in the first quadrant.

• CCW

Counterclockwise.

In CCW circular interpolation, X-axis operates in the minus direction and Y-axis operates in the plus direction in the first quadrant.

### 1.1.3 Notation

- (1) For the suffixes of pin names, register names, and bit names, "x" indicates the X-axis, "y" indicates the Y-axis, "z" indicates the Z-axis, and "u" indicates the U-axis. "N" indicates any axis.

- (2) Negative logic pins and negative logic signals are not indicated by overbars, or the like. For logic details, see "4.3 Functions of pins".

- (3) In the explanation of the bits of registers, "0" indicates that the bit is prohibited to use other than "0" when writing. Also, the bit is fixed at "0" when reading.

- (4) The specific bit of a status or a register is shown as "status name.bit name" or "register name.bit name".(For example, RMD.MSY represents MSY bit in RMD register.)

- (5) If there is a description of time, it shows a value at "Reference clock frequency = 19.6608 MHz" unless otherwise specified.

- (6) Regarding the signal status of "ON" or "OFF", "Rising edge", "H-level" or "1" indicates "ON" in the case of positive logic. "Falling edge", "L-level" or "0" indicates "ON" in the case of negative logic.

- (7) The numeric suffix "b" represents a binary number, and "h" represents a hexadecimal number.

No suffix is added to a decimal number.

Even if it is a binary or hexadecimal number, a suffix is not added in some graphs or when the binary or hexadecimal

- number is the same as the decimal number.

- (8) The consecutive bits are indicated by ":".(For example, MSTS [7:0] represents the 7th to 0th bits of MSTS.)

# 1.2 Handling the product

# 1.2.1 Storing

Store the product in an environment where condensation does not occur at a temperature from  $-65^{\circ}$ C to  $+150^{\circ}$ C.

# 1.2.2 Unpacking

Check if the quantity of the product you ordered, and moisture-proof desiccants are included in the package when unpacked.

### 1.2.3 Safety

This section describes the basic safety precautions for safer operations.

Follow the instructions below when using the product.

Failure to comply with the items may result in injuries or disasters.

#### 1.2.3.1 Precaution in design

| <ul> <li>consideration when designing your equipment. Additionally, never exceed the absolute maximum ratings, even for a very short time.</li> <li>Take precautions against the influence of heat in the environment and keep the temperature around the LSI as low as possible.</li> <li>Note that ignoring the following precautions may result in latching up and may cause overheating and smoke:</li> </ul>                  | 🛕 Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Fix the potential of unused input pins to V<sub>DD</sub> or GND, or pull them up or down.</li> <li>Pull up or down the potential of unused bidirectional pins.</li> <li>Do not short-circuit the outputs.</li> <li>Protect LSIs from induction, static electricity and the like from high voltage generatin circuits.</li> <li>Prevent LSIs from being applied overvoltage caused by a noise, serge, or static</li> </ul> | <ul> <li>Keep the operating voltage, operating temperature, input /output voltage/ current, etc. within the rated ranges. If used outside the rated range, it may increase the failure rate even if the LSI operates normally in the short term. Even within the rated range, the failure rate changes depending on the operating temperature and voltage. Take this into consideration when designing your equipment. Additionally, never exceed the absolute maximum ratings, even for a very short time.</li> <li>Take precautions against the influence of heat in the environment and keep the temperature around the LSI as low as possible.</li> <li>Note that ignoring the following precautions may result in latching up and may cause overheating and smoke: <ul> <li>Keep the voltage levels of input/output pins within the absolute maximum rated ranges.</li> <li>Please consider the timing of power-on.</li> <li>Be careful not to introduce external noise into LSIs.</li> <li>Fix the potential of unused input pins to V<sub>DD</sub> or GND, or pull them up or down.</li> <li>Pull up or down the potential of unused bidirectional pins.</li> <li>Do not short-circuit the outputs.</li> <li>Protect LSIs from induction, static electricity and the like from high voltage generating circuits.</li> </ul> </li> </ul> |

# 1.2.3.2 Precautions for transportation and storing LSIs

| 🛕 Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Always handle LSIs and the packages including LSIs with care. Do not throw or drop them. It may damage the LSIs or tear the aluminum-laminated packaging material and impair the airtightness.</li> <li>Do not store LSIs in a location exposed to water droplets or direct sunlight.</li> <li>Do not store LSIs in a location where corrosive gases are present or in excessively dusty environments.</li> <li>Store the LSIs in an anti-static storage container, and do not apply physical load to LSIs.</li> <li>Follow the caution signs and instructions on the packaging box when transporting or storing.</li> <li>The temperature and humidity of the storage location should be 30 ° C and 70% RH or less as a guide.</li> <li>Store in a place where there is minimal temperature fluctuation.</li> <li>Sudden changes in temperature during storage cause condensation, oxidation and corrosion of leads, and poor solder wettability.</li> <li>Install an antistatic mat on the surface of the storage shelf and ground the surface of the mat. (Resistance between surface and ground 7.5 x10<sup>6</sup> to 1 x10<sup>9</sup> ohm)</li> <li>When you remove LSIs from the packaging and then store them again, use an antistatic storage container.</li> </ul> |

| • When you remove LSIs from the packaging and then store them again, use an antistatic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

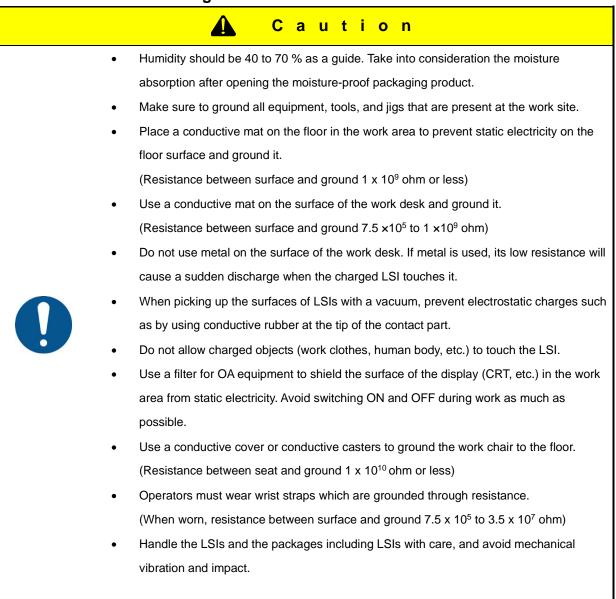

#### 1.2.3.3 Precautions for handling environment

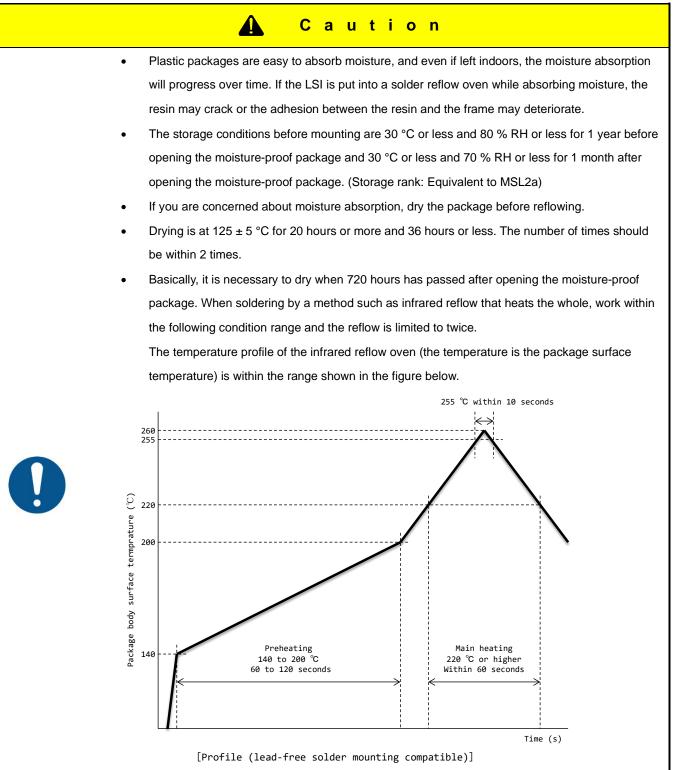

#### 1.2.3.4 Precautions for installation

- Soldering by the solder dipping method causes a sudden temperature change in the package. Avoid this method as it can damage the LSI.

- Perform manual soldering work using the soldering iron under the following conditions.

- The max temperature of the tip should be 350  $^\circ\text{C},$  within 5 seconds, and limited to twice.

- Be careful not to let the soldering iron come into contact with anything other than the leads, such as the package body.

# **1.3 Product Warranty**

This is the warranty of the product purchased from Nippon Pulse Motor. When the product is purchased from a supplier other than NPM, please contact that supplier regarding the product's warranty.

# 1.3.1 Warranty period

The warranty period is one year from the date of delivery to an assigned place.

### 1.3.2 Warranty scope

If any defect is found in a product during the warranty period under the normal use following this document, NPM will repair or replace the product without charge.

However, the following cases are not covered by the warranty even during the warranty period.

- 1) Products modified or repaired by anyone other than NPM or a person authorized by NPM.

- 2) Defects that result from dropping after the delivery or mishandling in transit.

- 3) Natural deterioration, wearing, and fatigue of components.

- 4) Defects result from any usage other than the original described in this manual.

- 5) Defects result from natural disaster or force majeure such as fires, earthquakes, lightning strikes, winds, floods, salts or electrical surges.

- 6) Defects or damages result from a cause that is not the fault of NPM.

# 1.4 Notice

This document aims to describe the details of functions of the product. It does not warrant fitness for a particular purpose of the customer. Also, the examples of applications and circuit diagrams in this manual are included only for your reference. Please confirm the features and the safety of device or equipment before use.

# 1.5 Confirmation

Please do not use this product in the following conditions. If you need to use in the following conditions, please contact our sales representatives:

- 1. Any equipment that may require a high reliability or a safety, such as nuclear facilities, electricity or gas supply systems, transportation facilities, vehicles, various safety systems, medical equipment, etc.

- 2. Any equipment that may directly affect human survival or property.

- 3. Usages under conditions or circumstances that are not specified in the catalog, manual, etc.

For applications that may cause serious damages to a human life or property due to failure of this product, ensure high reliability and safety by redundant design.

# 2. Outline

# 2.1 Features

PCL6046 is a 4-axis pulse control LSI for stepping motors and servo motors.

In the CMOS configuration, the connection with a CPU can be selected from four types of parallel bus interfaces.

In communication with a CPU, you can input commands, input/output data, and output signals such as interrupt requests.

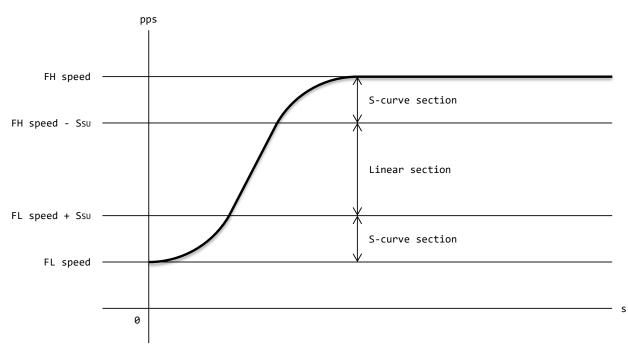

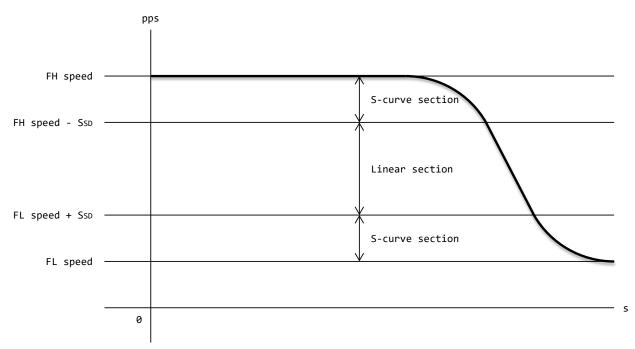

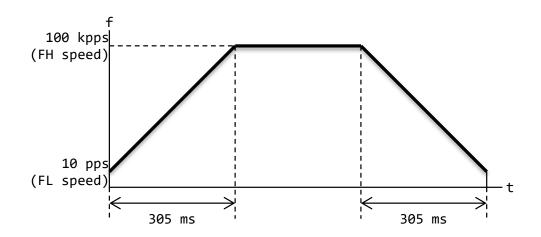

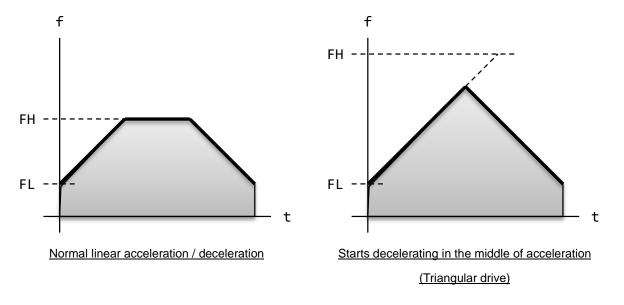

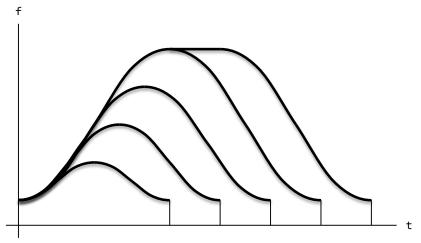

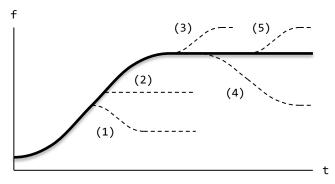

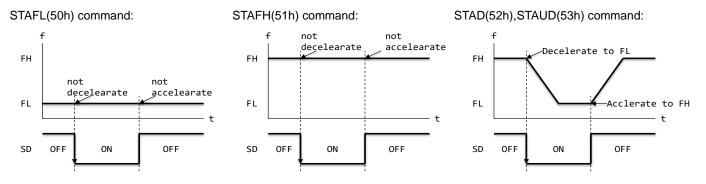

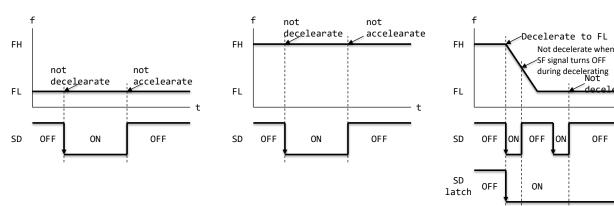

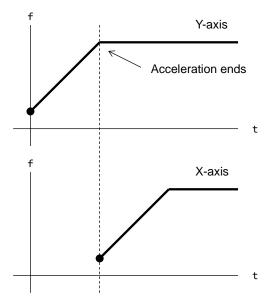

Motor speed can be controlled at constant speed or with acceleration/deceleration. For acceleration/deceleration, you can select either linear or S-curve.

Motor positioning can be controlled by continuous, set amount, or sensor signals.

#### - CPU interface

The following four types of CPU interface circuits are built-in.

- 1. 16-bit interface for 68000

- 2. 16-bit interface for H8

- 3. 16-bit interface for 8086

- 4. 8-bit interface for Z80

- Direct access to internal registers

When connecting all A9 to A0 pins, the register control command is not required.

In this case, you can access the internal registers directly in the 1024-byte address space.

A register control command is required when connecting A7 to A3 pins to VDD or GND.

In this case, you can access the internal registers indirectly only in the 32-byte address space.

- Acceleration/deceleration speed control

Linear acceleration/deceleration and S-curve acceleration/deceleration are available.

For S-curve acceleration/deceleration, linear acceleration/deceleration lines can be inserted in the middle by setting S-curve sections.

For S-curve section setting, acceleration and deceleration characteristics can be set independently.

You can perform S-curve deceleration after Linear acceleration, or vice versa.

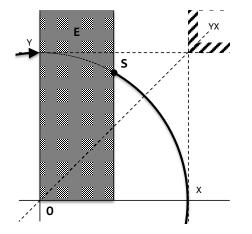

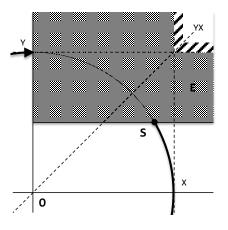

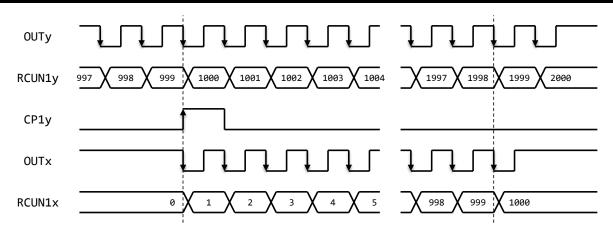

- Interpolation operation

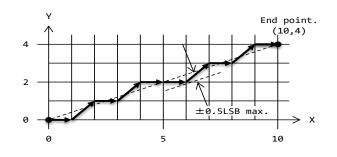

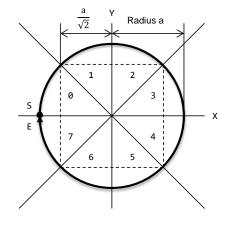

You can perform linear interpolation with any two to four axes, and circular interpolation with any two axes.

- Target speed override

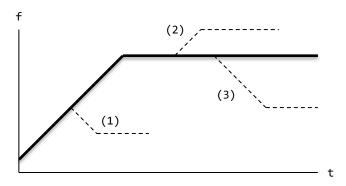

Target speed can be changed during operation.

However, if you avoid the triangular drive in automatic FH correction function, the target speed override will not work. If you set S-curve acceleration/deceleration and constant synthesized speed control function for interpolation control of two or more axes, the optimum slow-down point cannot be re-calculated. Set the acceleration/ deceleration characteristics to linear or set the constant synthesized speed control function to OFF.

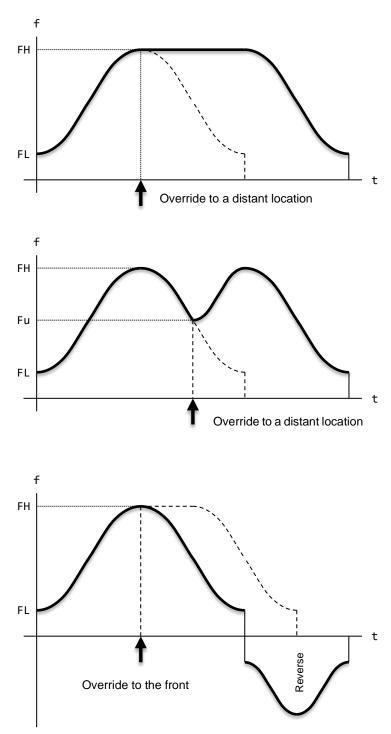

#### - Target position override

You can change the target position during operation.

- The following two types of target position override functions are built-in.

- 1) Target position (feed amount) can be changed while feeding in the positioning control.

- If the current position has exceeded the newly entered position, the motor will decelerate-stop (immediate stop in FL or FH constant speed pattern), and then move in the reverse direction.

- 2) Continuous movement is performed until PCS signal is input, and positioning control is performed when PCS signal is input.

- Triangle drive avoidance (FH correction function)

In the positioning mode, when there are a small number of output pulses, this function automatically lowers the maximum speed and avoids triangle driving.

- Pre-register

The 1st and 2nd data for continuous operation (feed amount, initial speed, feed speed, acceleration rate, deceleration rate, speed magnification rate, slow-down point, operation mode, center coordinate of circular interpolation, S-curve section in acceleration, S-curve section in deceleration, number of circular interpolation steps) can be written during operation. When the current operation mode is completed, the 1st data for continuous operation is automatically executed. In addition, 1st and 2nd data for continuous comparison can be written to the comparator as well.

#### - Counter

The following four counters are available for each axis.

| Counter   | Main purpose                                                                                      | Count target                                                                                                                                    |  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Counter 1 | Command position control (32 bit)                                                                 | Command pulse                                                                                                                                   |  |  |  |  |  |

| Counter 2 | Mechanical position control (32 bit)<br>(Can be used as a general-purpose<br>counter)             | Encoder<br>Command pulse<br>Manual pulser                                                                                                       |  |  |  |  |  |

| Counter 3 | Controlling the deviation between<br>the command position and the<br>mechanical position (16 bit) | Deviation between command pulse and encoder<br>Deviation between command pulse and manual pulser<br>Deviation between encoder and manual pulser |  |  |  |  |  |

| Counter 4 | IDX signal output (32 bit)<br>(Can be used as a general-purpose<br>counter)                       | Command pulse<br>Encoder<br>Manual pulser<br>1/2 cycle of reference clock                                                                       |  |  |  |  |  |

All counters can be cleared by writing a command or by inputting a CLR signal.

You can latch them by writing a command, or by inputting an LTC or ORG signal, and can clear them when latching.

The Counter 1, Counter 2, and Counter 4 have a ring count function that repeats counting through a specified counting range.

- Comparator

There are five comparators for each axis. They can compare the target values and counter values.

The count values to be compared can be selected from all four counters.

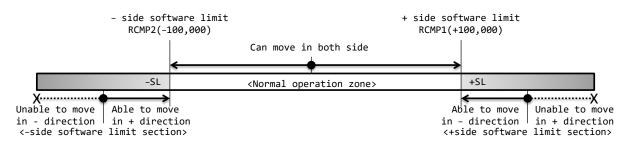

- Software limit function

You can set software limits using two circuits of the comparator.

When a motor enters the software limit range, the motor will stop immediately or decelerate-stop. After that motor can only move in the opposite direction to the previous movement.

- Backlash correction / Slip correction

Backlash correction corrects the feed amount each time the moving direction is changed. Slip correction corrects the feed amount regardless of the moving direction. However, the backlash correction cannot be applied even if the direction is changed while performing a circular interpolation.

- Index output

PCL6046 can output IDX signals at specified intervals.

#### - Simultaneous start

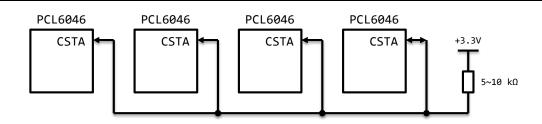

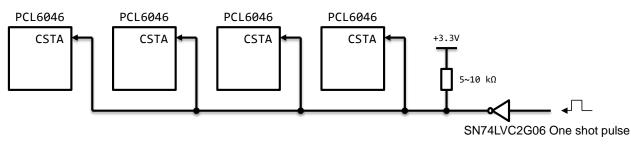

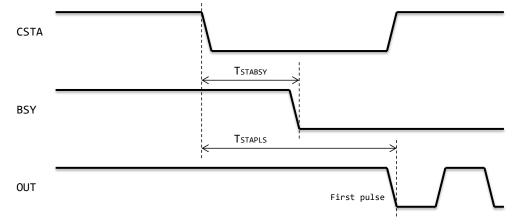

You can start any multiple axes simultaneously by writing a command or inputting a CSTA signal. Any multiple axes can be selected from multiple PCL6046s.

#### - Simultaneous stop

You can stop any multiple axes simultaneously by writing a command, inputting a CSTP signa, or by abnormal stopping of any axis. Any axis or any multiple axes can be selected from multiple PCL6046s.

#### - Vibration suppression

Specify a control constant in advance and add one pulse each for reverse and forward movement just before stopping. By adding the two pulses, vibration can be suppressed when stopping.

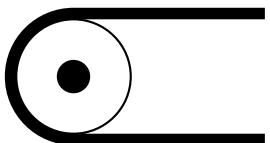

#### - Manual pulser input

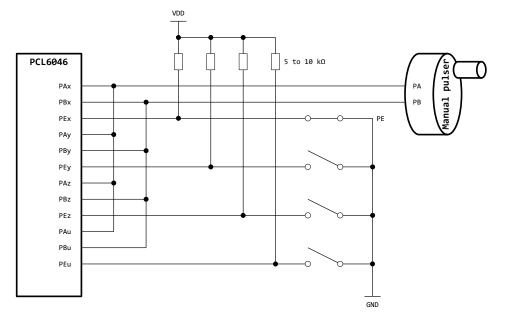

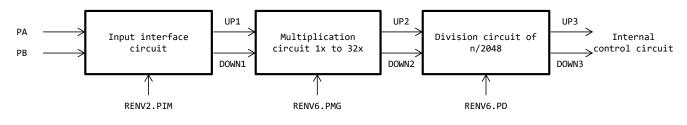

By applying manual pulse signals, you can rotate a motor directly in 1 pulse increment. The input signals can be either 90-degree phase difference signals (1x, 2x, or 4x) or up/down signals. For input signals, the magnification circuit of 1 to 32 times and the division circuit of  $\frac{1 \text{ to } 2048}{2048}$  are built-in. End limit (+ELn, -ELn) and software limit (+SL, -SL) settings are available. At each limit position, the command pulse is stopped, but the operation mode is not cancelled. Therefore, the command pulse output in the opposite direction can be continued.

- External switch input

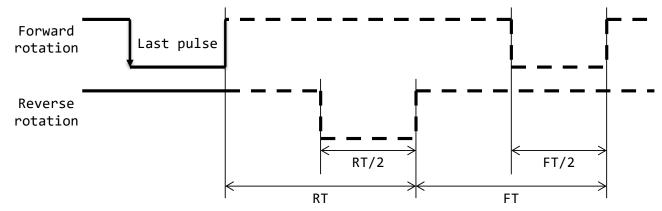

You can operate a motor directly in the direction of travel by inputting signals by an external switch. There are two input pins for the signals: forward rotation (+DRn) and reverse rotation (-DRn).

- Out-of-step detection

If the command pulse and encoder pulse are used for a counter (for deviation), out-of-step can be detected by a comparator.

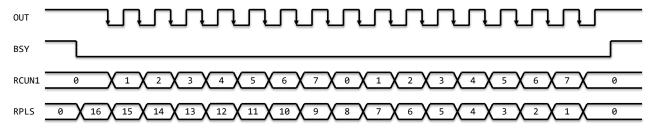

- Idling pulse output

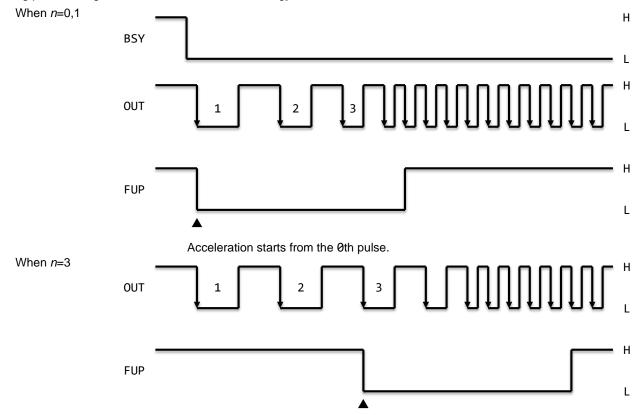

You can set the number of pulses to operate at the initial speed (FL) before accelerating to the operating speed (FH). You can also avoid out-of-step during acceleration by setting the self-starting frequency of a stepping motor to the initial speed.

#### - Operation mode

Various operation modes are built-in depending on the combination of control method, operation method, and functions.

<Examples of the operation modes>

- (1) Continuous movement in command control.

- (2) Continuous movement and incremental movement in pulser control.

- (3) Continuous movement and incremental movement in switch control.

- (4) Return to origin in sensor control.

- (5) Incremental movement of positioning control.

- (6) Incremental movement start in positioning control by CSTA signal.

- (7) Incremental movement start in positioning control by PCS signal.

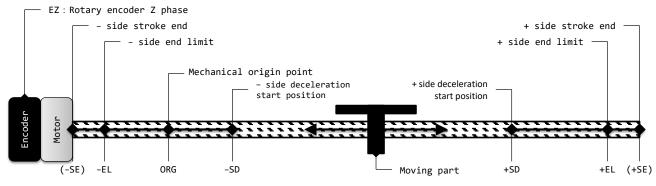

#### - Mechanical signal input

The following five signals can be input for each axis.

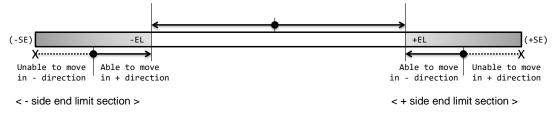

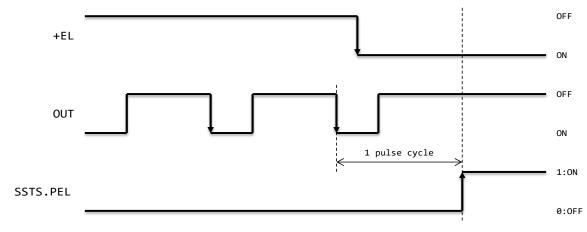

- +ELn: When this signal is turned ON, while moving in the positive (+) direction, movement on this axis stops immediately or decelerate-stop). When this signal is ON, no further movement occurs in the positive (+) direction. (The motor can be rotated in the negative (-) direction.)

- 2) -ELn: Functions the same as the +EL signal except that it works in the negative (-) direction.

- 3) +SDn: Decelerates or decelerate-stops according to the software settings. In the deceleration setting, if this signal is turned ON during high-speed operation, the speed will be decelerated to FL speed. Also, if this signal is already ON at the start, FL constant speed operation will be performed. In the deceleration stop setting, if this signal is turned ON during high-speed operation, the motor decelerates to FL speed and stop. Also, if this signal is already ON at the start, the motor will not operate.

- 4) -SDn: Similar to +SD signal, processed in the case of -direction operation.

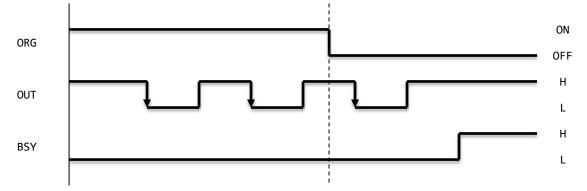

- 5) ORGn: Input signal for an origin return operation.

For safety, make sure +EL and -EL signals stay ON from the EL position until the end of each stroke.

The input logic for these signals can be changed using ELLn pin.

The input logic of +SD, -SD and ORG signals can be changed using software.

#### - Servomotor Interface

The following two signals can be input and one signal can be output:

- 1) INP: Inputs INP (positioning complete) signal that is output by a servo motor driver.

- 2) ERC: Outputs ERC (deviation counter clear) signal to a servomotor driver.

- 3) ALM: Inputs ALM (Alarm) signal that is output by a servomotor driver.

Regardless of the direction of operation, when this signal is ON, movement on this axis stops immediately or decelerate-stops. When this signal is ON at start, no movement occurs on this axis.

The input/output logic of INP, ERC, and ALM signals can be changed using software.

ERC signal is a pulse output. The pulse length can be set. (11 µs to 100 ms. A level output is also available.)

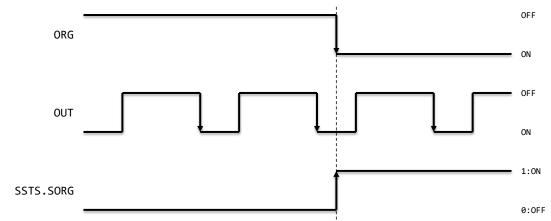

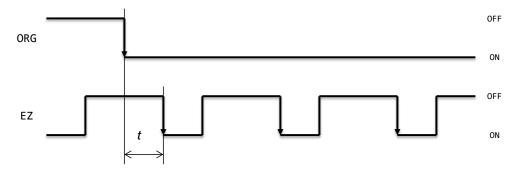

- Origin return sequences

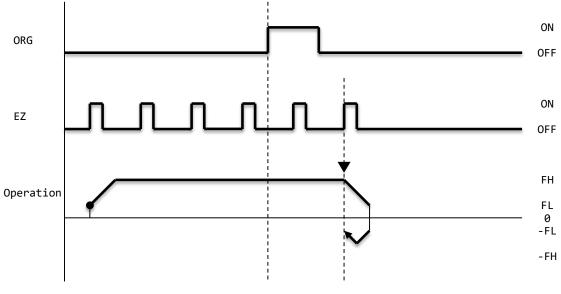

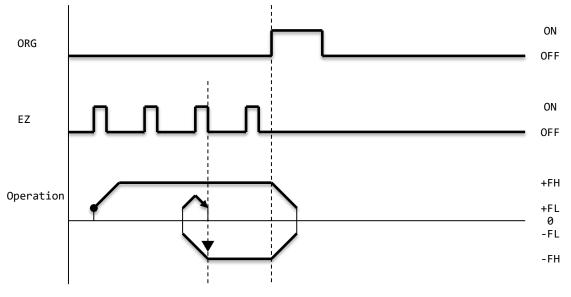

In sensor control, in addition to the origin (ORGn), the encoder Z-phase (EZn), end limit (+ELn, -ELn), and slowdown (+SDn, -SDn) can be combined to perform various origin return sequences.

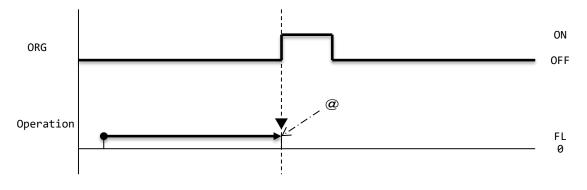

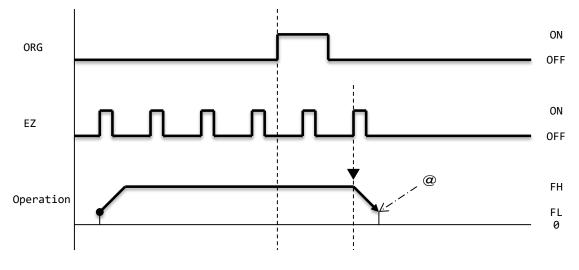

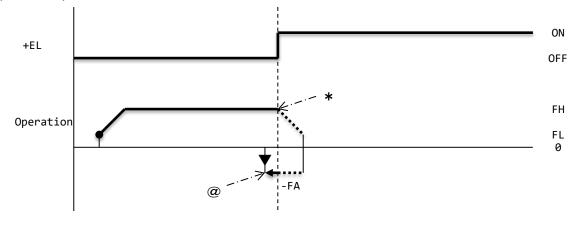

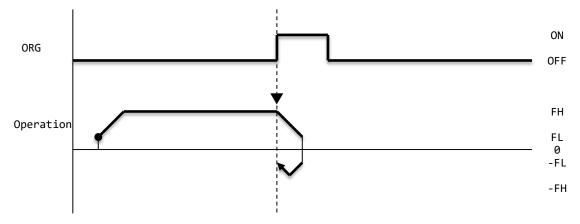

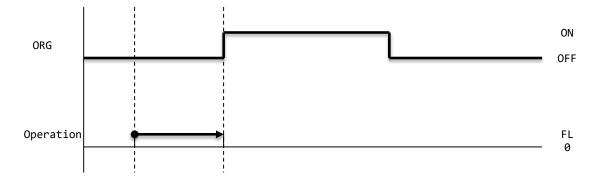

- 1) Stops when ORG signal is turned ON

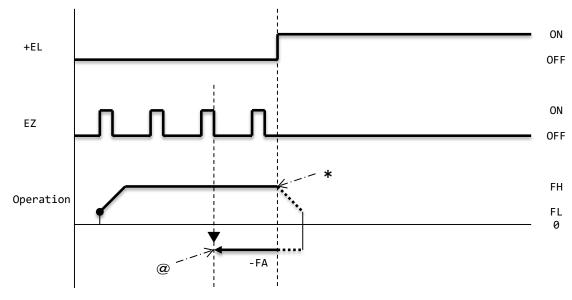

- 2) Stops when the specified number of EZ signals is counted after ORG signal is turned ON.

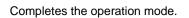

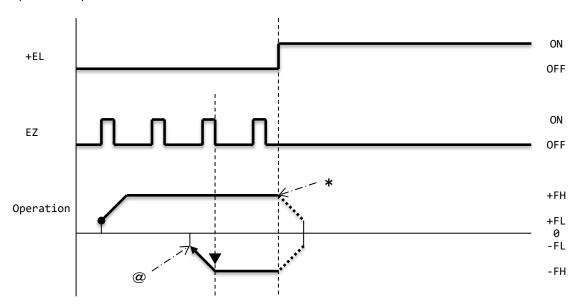

- 3) Stops when ORG signal turns ON. After reversing, stops when the specified number of EZ signals is counted.

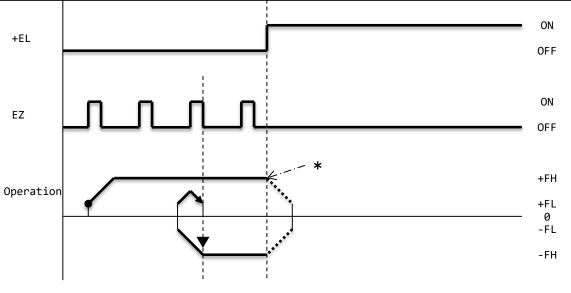

- 4) Stops when EL signal in the operating direction turns ON.

- 5) Stops when EL signal in the operating direction turns ON. After reversing, stops after the specified number of EZ signals is counted.

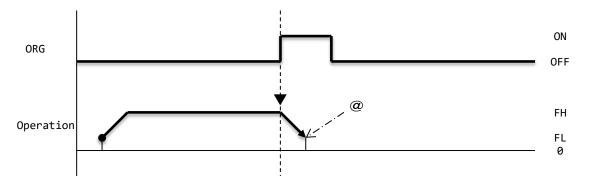

- 6) Decelerates when SD signal in the operating direction is ON and stops when the ORG signal is ON.

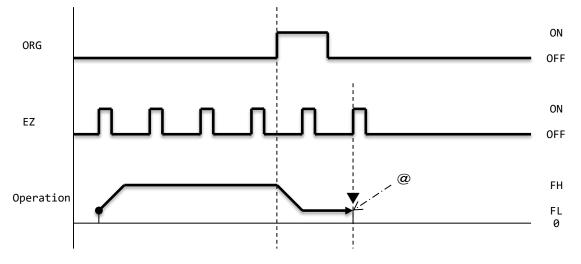

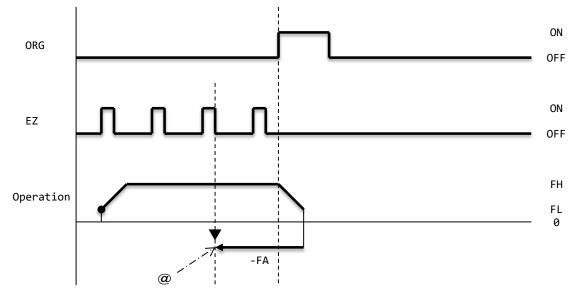

- 7) Decelerates when ORG signal turns ON and stops when the specified number of EZ signals is counted.

- 8) Decelerate-stops when ORG signal is ON. After reversing, stops after the specified number of EZ signals is counted.

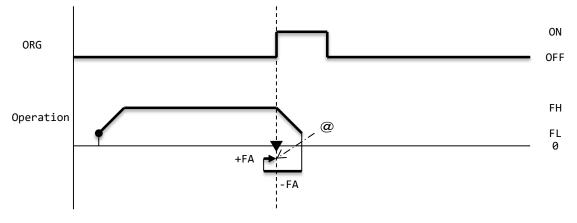

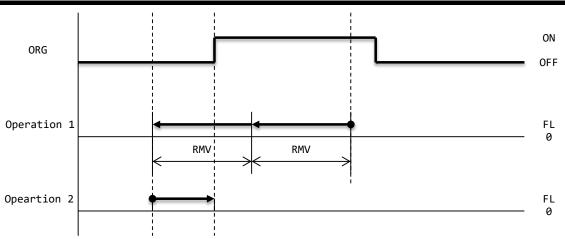

- 9) Decelerate-stops after ORG signal memorizes the ON position. After reversing, stops at the memorized position.

- 10) After ORG signal is turned ON, the position where the specified number of EZ signals is counted is memorized. Decelerates and stops. After reversing, stops at the memorized position.

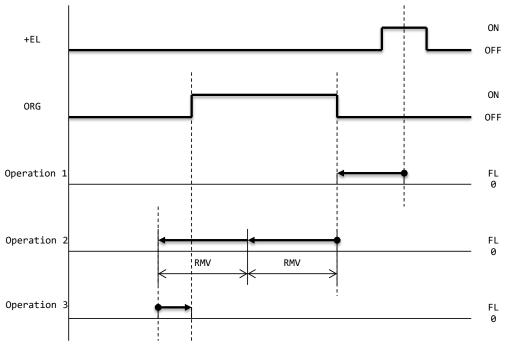

- 11) Decelerates and stops when EL signal in the operating direction is ON. After reversing, the position where the specified number of EZ signals is counted, and decelerate-stops. After reversing, stops at the memorized position.

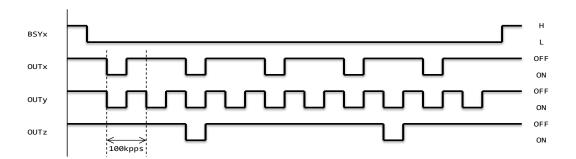

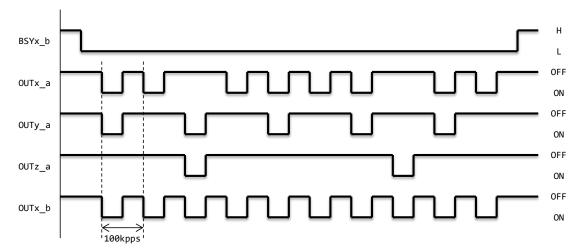

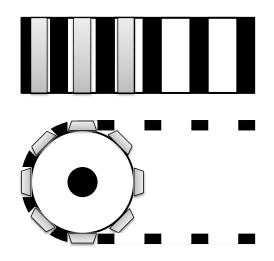

- Output pulse specifications

Output pulses can be selected among common-pulse mode (OUT/DIR), 2-pulse mode (PLS/MNS) or 90-degree phase difference mode (PHA/PHB). The output logic can also be selected.

In 90-degree phase difference mode, frequency of output signals reduces to 1/4 of operation speed.

Therefore, if the mode is selected, frequency characteristics of interface circuit can be lowered.

- Emergency stop input

When CEMG signal is turned ON, operation stops immediately. When this signal is ON at start, no movement is allowed.

- Interrupt request output

By various factors, L-level can be output from INT pin.

Output from INT pin by OR logic of each factor for each axis.

When more than one PCL6046 are used, wired OR connections are not possible.

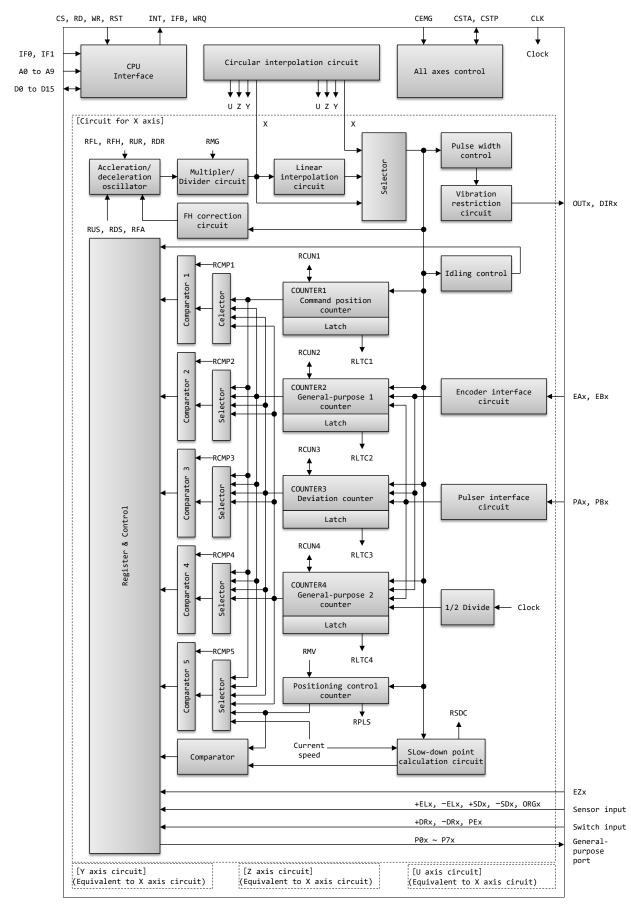

# 2.2 Configuration

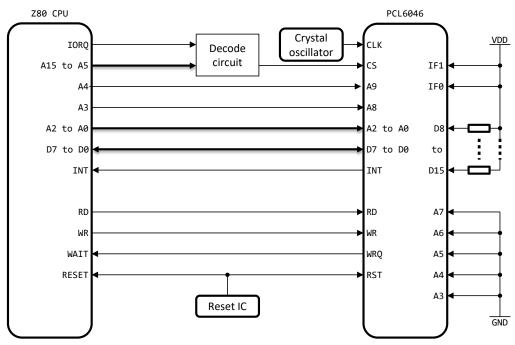

Controlling PCL6046 requires a crystal oscillator outputting recommended frequency of 19.6608 MHz and a CPU with a Parallel-

bus interface with a 16-bit or 8-bit data bus.

# 3. Specifications

The following table shows the specifications of PCL6046 such as the functions.

| Item                                                                       | Description                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Number of axes [axis]                                                      | 4 axes                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Positioning control range [pulses]                                         | -2,147,483,648 to +2,147,483,647 (32 bits)                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Number of registers used for setting speeds [ /axis]                       | 3 (FL, FH, and FA)                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Speed setting step number [steps]                                          | 1 to 65,535 (16 bits)                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|                                                                            | 0.1 to 100<br><examples 19.6608="" clock="" mhz="" of="" reference="" the=""></examples>                                                                                                                                              |  |  |  |  |  |  |  |  |

| Speed magnification range [times]                                          | Multiply by 0.1: 0.1 to 6,553.5 pps<br>Multiply by 1: 1 to 65,535 pps<br>Multiply by 100: 100 to 6,553,500 pps<br><example 30.0="" clock="" mhz="" of="" reference="" the=""><br/>Multiply by 152.5: 152.5 to 9,999,847 pps</example> |  |  |  |  |  |  |  |  |

| <u></u>                                                                    | (pps: pulse per second)                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Slow-down point setting range [pulses]                                     | 0 to 16,777,215 (24 bits)                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| S-curve deceleration characteristics S-curve deceleration can be combined. |                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Acceleration rate setting range [step <sup>-1</sup> ]                      | to 65,535 (16 bits)                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Deceleration rate setting range [step-1]                                   | 1 to 65,535 (16 bits)                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Counter [Circuit/axis]                                                     | 4:<br>Counter 1: Command position counter (32 bits)<br>Counter 2: General-purpose counter 1 (32 bits)<br>Counter 3: Deviation counter (16 bits)<br>Counter 4: General-purpose counter 2 (32 bits)                                     |  |  |  |  |  |  |  |  |

| Comparators [Circuit/axis]                                                 | 5 (32 bits)                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Interpolation functions                                                    | Linear interpolation: One set of any two or more axes, and one set of any one or more axes<br>Circular interpolation: One set of any two axes                                                                                         |  |  |  |  |  |  |  |  |

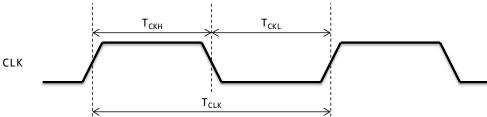

| Reference clock frequency [MHz] (f <sub>CLK)</sub>                         | 19.6608 (Max: 30 MHz)                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| CPU interface (Parallel-Bus)                                               | 68000 (16 bits), H8 (16 bits), 8086 (16 bits), Z80 (8 bits)                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Package type                                                               | 208 pin TFBGA                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Package size [mm]                                                          | 12 × 12 (Mold part)                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|                                                                            | 0.28 (typ.)                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Weight [g]                                                                 | 0.20 (()))                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Weight [g]<br>Power supply [V]                                             | Single power supply of 3.3 V                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|                                                                            |                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Power supply [V]                                                           | Single power supply of 3.3 V                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

# 4. Hardware description

The following shows the external dimensions and pin list. The connection between PCL6046 and a CPU is explained.

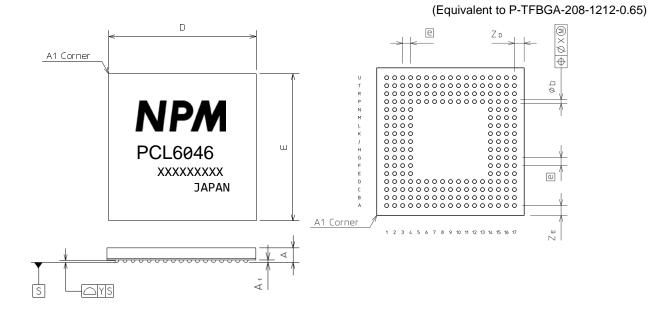

# 4.1 External dimensions

A1 pin is located at the upper left of PCL6046 marking.

| Symbol         | Dimension in Millimeters |         |         |  |  |  |  |  |  |  |

|----------------|--------------------------|---------|---------|--|--|--|--|--|--|--|

| Symbol         | Minimum                  | Nominal | Maximum |  |  |  |  |  |  |  |

| D              | 11.90                    | 12.00   | 12.10   |  |  |  |  |  |  |  |

| E              | 11.90                    | 12.00   | 12.10   |  |  |  |  |  |  |  |

| А              | -                        | -       | 1.20    |  |  |  |  |  |  |  |

| A <sub>1</sub> | 0.17                     | 0.22    | 0.27    |  |  |  |  |  |  |  |

| e              | -                        | 0.65    | -       |  |  |  |  |  |  |  |

| b              | 0.27                     | 0.32    | 0.37    |  |  |  |  |  |  |  |

| Х              | -                        | -       | 0.08    |  |  |  |  |  |  |  |

| Y              | -                        | -       | 0.10    |  |  |  |  |  |  |  |

| ZE             | 0.70                     | 0.80    | 0.90    |  |  |  |  |  |  |  |

| ZD             | 0.70                     | 0.80    | 0.90    |  |  |  |  |  |  |  |

# 4.2 Pin assignment diagram

TOP VIEW

|   | 1    | 2    | 3    | 4    | 5   | 6   | 7   | 8    | 9    | 10  | 11   | 12   | 13   | 14   | 15   | 16   | 17   |   |

|---|------|------|------|------|-----|-----|-----|------|------|-----|------|------|------|------|------|------|------|---|

| А | (NC) | GND  | ELLz | VDD  | GND | GND | PEz | LTCu | +DRu | EZu | LTCz | +DRz | PCSy | PBz  | EBz  | VDD  | (NC) | А |

| В | VDD  | ELLu | ELLy | CEMG | GND | CLK | PEy | CLRu | GND  | EBu | CLRz | GND  | -DRy | PAz  | EAz  | РВу  | GND  | В |

| С | IF0  | RST  | ELLx | CSTP | GND | VDD | PEx | PCSu | PBu  | EAu | PCSz | LTCy | +DRy | EZz  | EBy  | EZy  | PAy  | С |

| D | CS   | GND  | IF1  | CSTA | GND | PEu | GND | -DRu | PAu  | VDD | -DRz | CLRy | GND  | CLRx | LTCx | GND  | EAy  | D |

| Е | AØ   | GND  | WR   | RD   |     |     |     |      |      |     |      |      |      | VDD  | +DRx | -DRx | PCSx | Е |

| F | A4   | A3   | A2   | A1   |     |     |     |      |      |     |      |      |      | EBx  | EZx  | PAx  | PBx  | F |

| G | A7   | A6   | A5   | VDD  |     |     |     |      |      |     |      |      |      | ALMu | INPu | GND  | EAx  | G |

| Н | INT  | GND  | A9   | A8   |     |     |     |      |      |     |      |      |      | +SDu | -SDu | +ELu | -ELu | Н |

| J | D0   | VDD  | IFB  | WRQ  |     |     |     |      |      |     |      |      |      | ALMz | INPz | GND  | ORGu | J |

| К | GND  | D3   | D2   | D1   |     |     |     |      |      |     |      |      |      | +SDz | -SDz | +ELz | -ELz | к |

| L | D7   | D6   | D5   | D4   |     |     |     |      |      |     |      |      |      | ALMy | INPy | VDD  | ORGz | L |

| М | D10  | D9   | D8   | GND  |     |     |     |      |      |     |      |      |      | +SDy | -SDy | +ELy | -ELy | М |

| Ν | D13  | D12  | VDD  | D11  |     |     |     |      |      |     |      |      |      | ALMx | INPx | GND  | ORGy | Ν |

| Ρ | P0x  | GND  | D15  | D14  | P3y | P7y | P2z | P6z  | P1u  | P5u | OUTx | DIRy | VDD  | ERCx | -SDx | +ELx | -ELx | Ρ |

| R | P3x  | P2x  | P1x  | P0y  | P4y | GND | P3z | P7z  | P2u  | P6u | DIRx | GND  | OUTu | ERCy | GND  | ORGx | +SDx | R |

| Т | P5x  | P4x  | P7x  | P1y  | P5y | P0z | P4z | VDD  | P3u  | P7u | VDD  | OUTz | DIRu | ERCz | BSYx | BSYz | VDD  | т |

| U | (NC) | P6x  | VDD  | P2y  | P6y | P1z | P5z | P0u  | P4u  | GND | OUTy | DIRz | GND  | ERCu | BSYy | BSYu | (NC) | U |

|   | 1    | 2    | 3    | 4    | 5   | 6   | 7   | 8    | 9    | 10  | 11   | 12   | 13   | 14   | 15   | 16   | 17   |   |

# 4.3 Functions of pins

- 1. [I/O] column shows the direction of signals.

- I: Input, O: Output, B: Bidirectional.

- 2. [Logic] column shows the logic of signals.

- P: Positive logic, N: Negative logic, #: Can be changed by software, %: Set by hardware.

- 3. [Unuse] column shows the connection destination when not in use.

Open: Not connected, Vdd: VDD or pull-up connection, Pup: Pull-up connection.

Pull-up resistors of 5 to 10 kohm are recommended.

As described in "7.3 DC characteristics", some input pins and bidirectional pins have built-in pull-up resistors.

The built-in pull-up resistor is to prevent floating.

It is recommended to pull up outside to support noise resistance.

- 4. All signal input pins can input 0 to +5 V level.

- Output pins of all signals can be pulled up to +5 V, but cannot output more than VDD.

A pull-up resistor value of 5 kohm or higher is recommended.

| Signal name | Ball No.      | I/O | Logic | Unuse | Description                                             |

|-------------|---------------|-----|-------|-------|---------------------------------------------------------|

|             | A2, A5,       |     |       |       | Power supply pin connected to GND                       |

|             | A6, B5,       |     |       |       | Connect all GND pins to GND power supply.               |

|             | B9, B12, B17, |     |       |       |                                                         |

|             | C5, D2, D5,   |     |       |       |                                                         |

| GND         | D7, D13, D16, |     |       |       |                                                         |

| GND         | E2, G16, H2,  | -   | -     | -     |                                                         |

|             | J16, K1, M4,  |     |       |       |                                                         |

|             | N16, P2, R6,  |     |       |       |                                                         |

|             | R12, R15,     |     |       |       |                                                         |

|             | U10, U13      |     |       |       |                                                         |

|             | A4, A16, B1,  |     |       |       | Power supply pin connected to +3.3 V                    |

|             | C6, D10, E14, |     |       |       | Connect all VDD pins to +3.3 V power supply.            |

| VDD         | G4, J2, L16,  | -   | -     | -     |                                                         |

|             | N3, P13, T8,  |     |       |       |                                                         |

|             | T11, T17, U3  |     |       |       |                                                         |

| RST         | C2            |     | N     | _     | Input pin for the hardware reset signal                 |

|             | 02            | 1   | IN    | -     | For details, see "6.1.1 Hardware reset".                |

|             |               |     |       |       | Input pin for the reference clock signal                |

| CLK         | B6            | I   | Р     | -     | Connect a crystal oscillator outputting the recommended |

|             |               |     |       |       | frequency of 19.6608 MHz.                               |

| Signal name | Ball No. | I/O | Logic | Unuse | Description                                               |  |  |  |  |  |  |

|-------------|----------|-----|-------|-------|-----------------------------------------------------------|--|--|--|--|--|--|

|             |          |     |       |       | Input pins for CPU interface selection                    |  |  |  |  |  |  |

|             |          |     |       |       | CPU interface IF1 IF0 RD WR A0 WRQ                        |  |  |  |  |  |  |

| IF0,        | C1       |     |       |       | 68000(16 bit) L L VDD R/W LDS DTACK                       |  |  |  |  |  |  |

| IF1         | D3       | I   | Р     | -     | H8(16 bit) L H RD HWR GND WAIT                            |  |  |  |  |  |  |

|             | 20       |     |       |       | 8086(16 bit) H L RD WR GND READY                          |  |  |  |  |  |  |

|             |          |     |       |       | Z80(8 bit) H H RD WR AØ WAIT                              |  |  |  |  |  |  |

|             |          |     |       |       | Input pin for chip selection signal                       |  |  |  |  |  |  |

| cs          | D1       | I   | N     | -     | Enable RD and WR pins at $CS = L$ level.                  |  |  |  |  |  |  |

|             |          |     |       |       | Input pin for read signal                                 |  |  |  |  |  |  |

| RD          | E4       |     | N     | -     | Enable RD pin at CS = L level.                            |  |  |  |  |  |  |

|             |          |     |       |       | Input pin for the write signal                            |  |  |  |  |  |  |

| WR          | E3       |     | N     | -     | Enable WR pin at CS = L level.                            |  |  |  |  |  |  |

| A0, A1,     | E1, F4,  |     |       |       | Input pins for address signal                             |  |  |  |  |  |  |

| A2, A3,     | F3, F2,  |     |       |       | For the reduced address method, connect A3 to A7 pins to  |  |  |  |  |  |  |

| A4, A5,     | F1, G3,  | I   | Р     | -     | VDD or GND by selecting CPU interface. If IF1 = L level,  |  |  |  |  |  |  |

| A6, A7,     | G2, G1,  |     |       |       | connect VDD. If IF1 = H level, connect GND.               |  |  |  |  |  |  |

| A8, A9      | H4, H3   |     |       |       |                                                           |  |  |  |  |  |  |

| INT         | H1       | 0   | N     | Open  | Output pin for interrupt request signal                   |  |  |  |  |  |  |

|             |          | U   |       | Open  | See "6.18 Interrupt request (INT)" for details.           |  |  |  |  |  |  |

| WRQ         | J4       | 0   | Ν     | Open  | Output pin for wait request signal                        |  |  |  |  |  |  |

| IFB         | J3       | 0   | Ν     | Open  | Output pin for interface running signal                   |  |  |  |  |  |  |

| D0, D1,     | J1, K4,  |     |       |       | Bit0 to Bit7 of the data bus are connected.               |  |  |  |  |  |  |

| D2, D3,     | K3, K2,  | В   | Р     | _     |                                                           |  |  |  |  |  |  |

| D4, D5,     | L4, L3,  |     |       |       |                                                           |  |  |  |  |  |  |

| D6, D7      | L2, L1   |     |       |       |                                                           |  |  |  |  |  |  |

| D8, D9,     | M3, M2,  |     |       |       | Bit8 to Bit15 of the data bus are connected.              |  |  |  |  |  |  |

| D10, D11,   | M1, N4,  | в   | Р     | Pup   | For Z80-Bus (8bit), pull-up connection is required.       |  |  |  |  |  |  |

| D12, D13,   | N2, N1,  |     |       |       |                                                           |  |  |  |  |  |  |

| D14, D15    | P4, P3   |     |       |       |                                                           |  |  |  |  |  |  |

| CSTA        | D4       | В   | N     | Pup   | CSTA signal input/output pin                              |  |  |  |  |  |  |

|             |          |     |       |       | See "6.9.1 Simultaneous start (CSTA)" for details.        |  |  |  |  |  |  |

| CSTP        | C4       | В   | N     | Pup   | CSTP signal input/output pin                              |  |  |  |  |  |  |

|             |          |     |       |       | See "6.10 External stop / simultaneous stop" for details. |  |  |  |  |  |  |

| CEMG        | B4       |     | N     | Vdd   | CEMG signal input pin                                     |  |  |  |  |  |  |

|             | -        |     |       | vuu   | See "6.11 Emergency stop " for details.                   |  |  |  |  |  |  |

| Signal name | Ball No. | I/O | Logic | Unuse     | Description                                                 |

|-------------|----------|-----|-------|-----------|-------------------------------------------------------------|

| ELLx,       | СЗ,      |     |       |           | Input pins to set the input logic of +EL and -EL signals    |

| ELLy,       | ВЗ,      | 1   | N     | Vdd       | See "6.7.1 End limit (+EL, -EL)" for details.               |

| ELLz,       | АЗ,      | I   | IN    | vuu       |                                                             |

| ELLu        | B2       |     |       |           |                                                             |

| +ELx,       | P16,     |     |       |           | +EL signal input pins                                       |

| +ELy,       | M16,     |     | N10/  | Vdd       | See "6.7.1 End limit (+EL, -EL)" for details.               |

| +ELz,       | K16,     | I   | N%    | vaa       |                                                             |

| +ELu        | H16      |     |       |           |                                                             |

| -ELx,       | P17,     |     |       |           | -EL signal input pins                                       |

| −ELy,       | M17,     |     | N107  | Valal     | See "6.7.1 End limit (+EL, −EL)" for details.               |

| -ELz,       | K17,     | I   | N%    | Vdd       |                                                             |

| -ELu        | H17      |     |       |           |                                                             |

| +SDx,       | R17,     |     |       |           | +SD signal input pins                                       |

| +SDy,       | M14,     |     | N1//  | Vdd       | See "6.7.2 Slow-down (+SD, −SD)" for details.               |

| +SDz,       | K14,     | I   | N#    |           |                                                             |

| +SDu        | H14      |     |       |           |                                                             |

| -SDx,       | P15,     |     |       |           | −SD signal input pins                                       |

| −SDy,       | M15,     |     | N1#   | ) ( al al | See "6.7.2 Slow-down (+SD, −SD)" for details.               |

| -SDz,       | K15,     | I   | N#    | Vdd       |                                                             |

| -SDu        | H15      |     |       |           |                                                             |

| ORGx,       | R16,     |     |       |           | ORG signal input pins                                       |

| ORGy,       | N17,     |     | N1#   | Valal     | See "6.7.3 Origin (ORG), encoder Z phase (EZ)" for details. |

| ORGz,       | L17,     | I   | N#    | Vdd       |                                                             |

| ORGu        | J17      |     |       |           |                                                             |

| ALMx,       | N14,     |     |       |           | ALM signal input pins                                       |

| ALMy,       | L14,     |     | N#    | Vdd       | Connect to the servo motor driver.                          |

| ALMz,       | J14,     | I   | IN#   | vaa       | See "6.8.3 Alarm (ALM)" for details.                        |

| ALMu        | G14      |     |       |           |                                                             |

| OUTx,       | P11,     |     |       |           | Command pulse signal output pins                            |

| OUTy,       | U11,     | ~   | O N#  | 0.555     | See "6.5 Output pulse control" for details.                 |

| OUTz,       | T12,     | 0   |       | Open      |                                                             |

| OUTu        | R13      |     |       |           |                                                             |

| DIRx,       | R11,     |     |       |           | The output pins for the command pulse signal.               |

| DIRy,       | P12,     | ~   | NIΨ   | 0.555     | See "6.5 Output pulse control" for details.                 |

| DIRz,       | U12,     | 0   | N#    | Open      |                                                             |

| DIRu        | T13      |     |       |           |                                                             |

| Signal name | Ball No. | I/O | Logic | Unuse | Description                                                        |

|-------------|----------|-----|-------|-------|--------------------------------------------------------------------|

| EAx,        | G17,     |     |       |       | Encoder A phase signal input pins                                  |

| EAy,        | D17,     | 1   |       | Vdd   | See "6.12.1 Counter type and input specifications" for details.    |

| EAz,        | B15,     | 1   | -     | vuu   |                                                                    |

| EAu         | C10      |     |       |       |                                                                    |

| EBx,        | F14,     |     |       |       | Encoder B phase signal input pins                                  |

| EBy,        | C15,     |     |       | Vdd   | See "6.12.1 Counter types and input specifications" for details.   |

| EBz,        | A15,     | I   | -     | Vdd   |                                                                    |

| EBu         | B10      |     |       |       |                                                                    |

| EZx,        | F15,     |     |       |       | Encoder Z-phase signal input pins                                  |

| EZy,        | C16,     |     | N#    | Vdd   | See "6.7.3 Origin (ORG), encoder Z phase (EZ)" for details.        |

| EZz,        | C14,     | I   | IN#   | vaa   |                                                                    |

| EZu         | A10      |     |       |       |                                                                    |

| PAx,        | F16,     |     |       |       | Manual pulser A-phase signal input pins                            |

| PAy,        | C17,     |     |       | Vdd   | See "5.5.3 Pulser control" for details.                            |

| PAz,        | B14,     | I   | -     |       |                                                                    |

| PAu         | D9       |     |       |       |                                                                    |

| PBx,        | F17,     |     |       |       | Manual pulser B-phase signal input pins                            |

| PBy,        | B16,     |     |       |       | See "5.5.3 Pulser control" for details.                            |

| PBz,        | A14,     | I   | -     | Vdd   |                                                                    |

| PBu         | C9       |     |       |       |                                                                    |

| PEx,        | C7,      |     |       |       | Input pins for manual pulser and external switch valid signals     |

| PEy,        | B7,      |     | N     | Vdd   | See "5.5.3 Pulser control" and "5.5.4 Switch control" for details. |

| PEz,        | A7,      | I   | N     | Vdd   |                                                                    |

| PEu         | D6       |     |       |       |                                                                    |

| +DRx,       | E15,     |     |       |       | +DR signal input pins                                              |

| +DRy,       | C13,     |     | N#    | Vdd   | See "5.5.4 Switch control" for details.                            |

| +DRz,       | A12,     | I   | IN#   | vaa   |                                                                    |

| +DRu        | A9       |     |       |       |                                                                    |

| -DRx,       | E16,     |     |       |       | -DR signal input pins                                              |

| -DRy,       | B13,     |     | N#    | Vdd   | See "5.5.4 Switch control" for details.                            |

| -DRz,       | D11,     | I   | IN#   | vaa   |                                                                    |

| -DRu        | D8       |     |       |       |                                                                    |

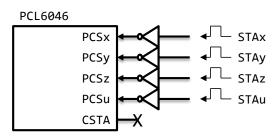

| PCSx,       | E17,     |     |       |       | Input pins for PCS and STA signals.                                |

| PCSy,       | A13,     |     | N#    | Vdd   | See "6.4.2 Target position override 2 (PCS)" and                   |

| PCSz,       | C11,     | I   | IN#   | vaa   | "6.9.2 Own axis start (STA)" for details.                          |

| PCSu        | C8       |     |       |       |                                                                    |

| Signal name     | Ball No. | I/O | Logic    | Unuse   | Description                                                    |

|-----------------|----------|-----|----------|---------|----------------------------------------------------------------|

| INPx,           | N15,     |     |          |         | INP signal input pins                                          |

| INPy,           | L15,     |     | N1#      | Vdd     | Connect to a servo motor driver.                               |

| INPz,           | J15,     | 1   | N#       | vaa     | See "6.8.1 Positioning complete (INP)" for details.            |

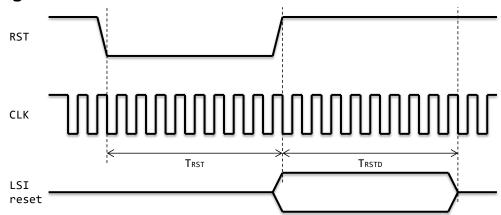

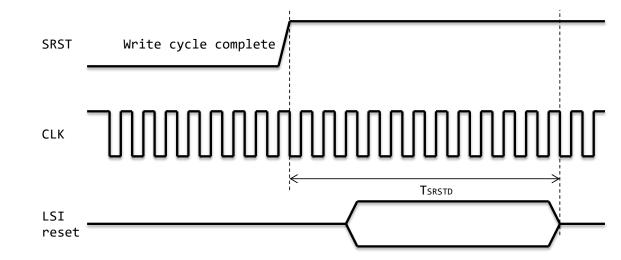

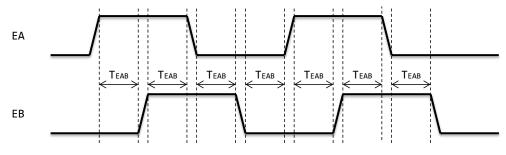

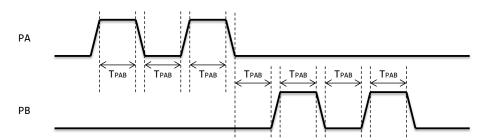

| INPu            | G15      |     |          |         |                                                                |